當前,全世界主要半導體研發機構和企業都在SOT-MRAM刻蝕工藝上開展了大量工作,然而,SOT-MRAM的刻蝕工藝依然是業界面臨的一項重要技術挑戰。

近日,中科院微電子所在SOT-MRAM的關鍵集成技術領域取得新進展。

據“中科院微電子研究所”消息,為了更好地解決SOT-MRAM的刻蝕技術難題以實現SOT-MTJ的高密度片上集成,同時研究不同的刻蝕工藝對器件磁電特性的影響,中國科學院微電子研究所集成電路先導工藝研發中心羅軍研究員課題組開發了一種基于垂直磁各向異性SOT-MTJ的刻蝕“停MgO”工藝(SOMP-MTJ),該工藝有效地解決了SOT-MRAM制造中的刻蝕短路問題。

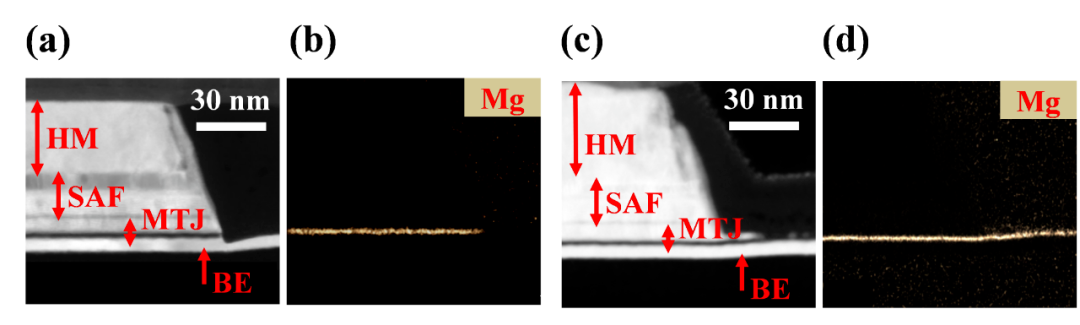

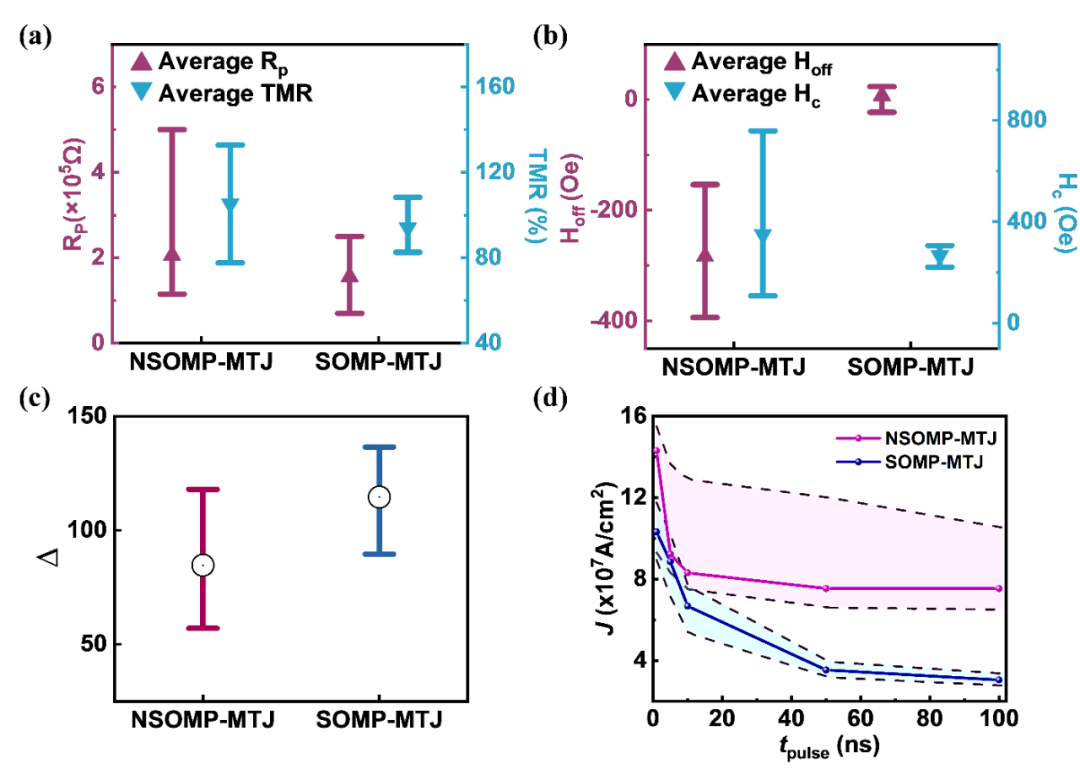

消息稱,課題組開發了刻蝕“停MgO”工藝,該工藝使MTJ刻蝕終點精確地停止在~1 nm厚的MgO層上(圖 1c,d)。由于隧穿層MgO的側壁從未暴露,從而避免了MgO層的短路。利用“停MgO”刻蝕工藝制備的SOT-MTJ器件陣列,晶圓的電阻良率可提升至100%,同時還提高了器件的TMR、電阻、矯頑力等關鍵參數的均勻性(圖 2a,b)。

另外,“停MgO”器件還具有更高的熱穩定性、更低的翻轉電流密度以及高達1 ns的翻轉速度(圖 2c,d)。該研究成果為高速、低功耗、高集成度SOT-MRAM的刻蝕技術問題提供了關鍵解決方案。

來源:中科院微電子研究所